---+ An Introduction to the Cryoelectronics Board

Contact author for this document: Graeme Smecher

This guide should provide you with instructions on how to safely un-package your boards, power them, and ascertain that the boards are functional.

Please remember that the McGill Cosmology Instrumentation Lab is NOT a for-profit company(!), we provide readout electronics to the projects we are scientifically involved with and occasionally to others on a cost recovery basis. If you have paid for boards, you have paid only for hardware. As a university, we are unable to provide any warranty whatsoever. Software and firmware are not deliverables with the boards and are provided on a voluntary basis under the relevant license(s). The support we provide is voluntary as well - please look carefully through the twiki documentation before asking questions, as we prefer to focus our time on new development and doing cosmology(!).

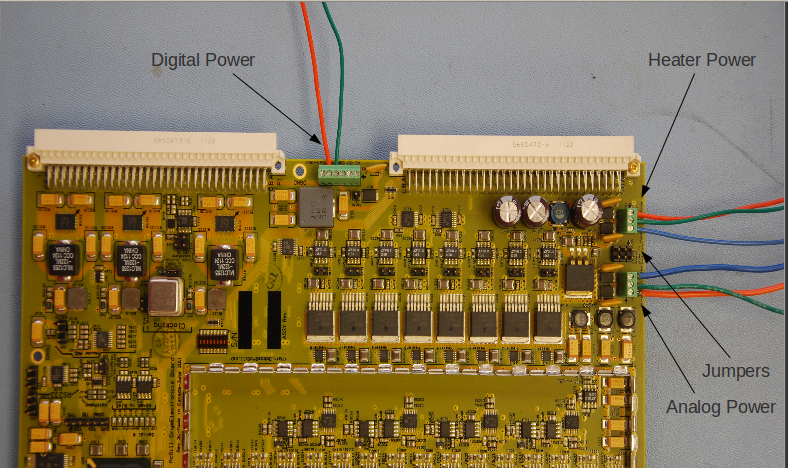

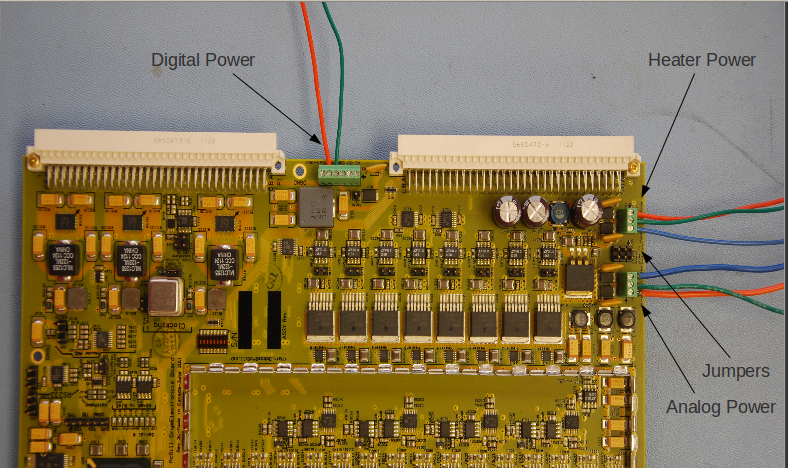

Fig. 1 shows the top of the cryoelectronics board, with major subsystems and connectors labeled.

Hardware

The major parts of the board are:

- A Spartan-6 FPGA

- A 16-channel thermometry controller

- An 8-channel heater controller

- Ethernet, RS-485, RS-232, and LVDS connectivity

- 64 MB of on-board DDR SDRAM

- 8 MB of on-board SPI flash (for bitstream storage)

- A MicroSD slot (for software storage)

The following sections describe basic care and feeding of these subsystems.

Clocking

The board operates on a 25 MHz clock, supplied over the VME backplane or using an on-board oscillator (the silver can just below the voltage regulators in Fig. 1.) The clock source is configured via jumpers. These jumpers are identical to those on the DfMUX (although they are likely numbered differently.)

The clock should be configured as follows:

When installing a local oscillator, you must align the tab on one corner of the can with the diagonal stripe shown on the board's silkscreen layer. (Getting the oscillator alignment wrong will likely blow up the oscillator.)

Jumpers

There are a number of miscellaneous (non-clock-related) jumpers on the board. They should be configured as follows:

Power

There are a number of power supplies on the board, with three ground planes:

- Sensor power and ground (Analog power),

- Heater power and ground

- Digital power and ground

Each of these islands is powered from positive and negative supplies and regulated before use. In the simplest configuration, the three power islands can be connected together and powered using one +5.7V supply and -5.7V supply. Fig. 1 shows such a configuration:

- Power enters the board using power header at the rear

- The sensor circuitry is connected to external power via three on-board jumpers (J30)

- The heater circuitry is powered from sensor power via the short wires visible at the upper-right side of Fig. 1.

Two other possible configurations are shown in figures 2 and 3. In figure 2, the digital, analog and heater powers are all separate. Note that the jumpers (J30) are left open.

|

| Fig 2. Separate power supplies |

|

| Fig 3. Sharing Digital and Analog power |

In figure 3, the digital and analog share the power lines (at J4). Note that the jumpers (J30) are shorted in this case.

When running in a crate the digital power will be connected from the backplane. You can short jumpers (J30), to use this for the analog power, or leave them open and provide external power to the connectors J4.

BE VERY CAREFUL

BE VERY CAREFUL when setting up the board's power. There are probably simple ways to cook your board (or crate) by getting this wrong, and we try our best not to discover them. Please do the same.

Gain Resistors.

Slots J1 and J3 allow the user to select the drive and sense gains for each thermometry channel on the board. The gain is a function of resistance, given by

%MATHMODE{ Gain = 1 + (49.3 k\Omega / Resistance) }%

It is recommended that the gain resistors be chosen such that the amplified signal is on the order of 0.1 mV. For the drive circuit, this voltage is measured across a 100 k resistor, so %MATHMODE{ V = G \times I_{bias} \times 100 k }% For the sense circuit, this voltage will be measured across the RTD.

At McGill the sensor channels with cold CERNOX thermometers have a drive gain set to gain 100 (500 Ohms), and a sense gain set to 500 (100 Ohms).

For stability reasons, do not set the drive gain higher than 165 (300 Ohms).

Software

On power-up, the board's FPGA needs to be configured before it can do anything. It does so from the SPI flash immediately behind the MicroSD slot. This SPI flash is programmed as part of McGill's quality-control procedures, and should rarely require an upgrade.

Otherwise, all of the board's firmware and software resides on a removable MicroSD card. This card can be reprogrammed or configured on a PC running Linux.

IP Address

By default, the board's IP address is automatically configured via DHCP. To change this, you can modify the Ethernet configuration using a Linux PC. You'll need to edit the

/etc/network/interfaces file on the board. By default, it looks like the following:

1 auto lo

2 iface lo inet loopback

3

4 # The primary network interface

5 auto eth0

6 iface eth0 inet dhcp

7 # address 192.168.0.10

8 # netmask 255.<span style="font-size: 12pt;">255.255.0</span>

9 # network 192.168.0.0

10 # broadcast 192.168.0.255

11 # gateway 192.168.0.1

A static configuration should look something like the following: (line numbers have been added for clarity, but don't belong in the file!)

1 auto lo

2 iface lo inet loopback

3

4 # The primary network interface

5 auto eth0

6 iface eth0 inet static

7 address 192.168.0.10

8 netmask 255.255.255.0

9 network 192.168.0.0

10 broadcast 192.168.0.255

11 gateway 192.168.0.1

Lastly, change the hardware address of the board to match its unique IP address. Run /sbin/ifconfig eth0 for the board and change the last octet to match the last three digits of the IP address.

1 auto lo

2 iface lo inet loopback

3

4 # The primary network interface

5 auto eth0

6 iface eth0 inet static

7 address 192.168.0.10

8 netmask 255.255.255.0

9 headdress ether 00:0A:35:27:A8:0A

10 network 192.168.0.0

11 broadcast 192.168.0.255

12 gateway 192.168.0.1

This topic: CryoElectronics

> WebHome > CryoBoardIntroduction

Topic revision: r9 - 2014-09-05 - JamesKennedy

BE VERY CAREFUL when setting up the board's power. There are probably simple ways to cook your board (or crate) by getting this wrong, and we try our best not to discover them. Please do the same.

BE VERY CAREFUL when setting up the board's power. There are probably simple ways to cook your board (or crate) by getting this wrong, and we try our best not to discover them. Please do the same.